It is a well-known fact that manufacturing test strategies must involve a combination of inspection, structural, and functional test technologies in order to yield highest quality and minimize customer returns. But a new breed of non-intrusive, software-based technologies promises to disrupt legacy test solutions by guaranteeing the highest test coverage at the lowest cost. These technologies leverage off of the embedded instruments within silicon to achieve this goal in the following ways…

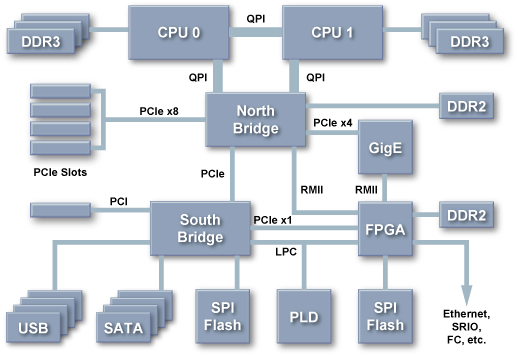

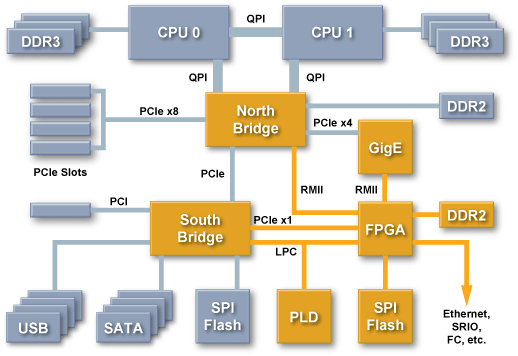

First of all, let’s look at an arbitrary printed circuit board design for a router or storage system. Let’s say this design contains one or more CPUs (which perform, for example, router control plane management and other duties). Then there’s a NorthBridge and SouthBridge which perform memory control and I/O fanout. There’s an assortment of devices which act as controllers (MAC, PHY) for USB, SATA, Ethernet, Serial RapidIO, and other interfaces. Finally, there’s the memory itself, an FPGA also acting as a service processor, and other glue logic on the board.

An example PCB

A design of this type may not be amenable to legacy probe-based structural testing by technologies such as ICT or Flying Probe. Large BGAs with heat sinks, blind and buried vias, extremely dense layouts and a plethora of high-speed I/O circuits may make the placement of test pads problematic.

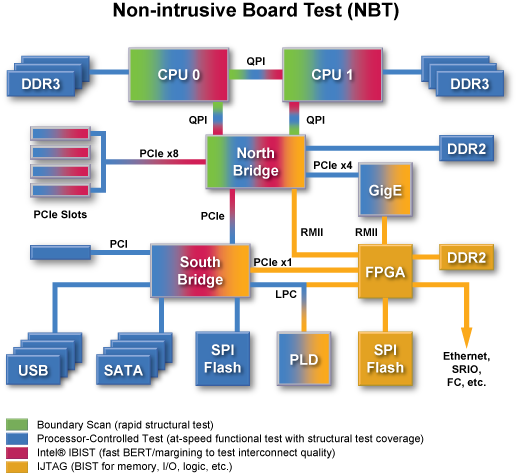

The alternative is to use a combination of software-based test technologies which circumvents the need for test points. Four of these technologies would include boundary scan, processor-controlled test, Intel® IBIST, and IJTAG-based MBIST and IOBIST. Let’s look at each of these in turn.

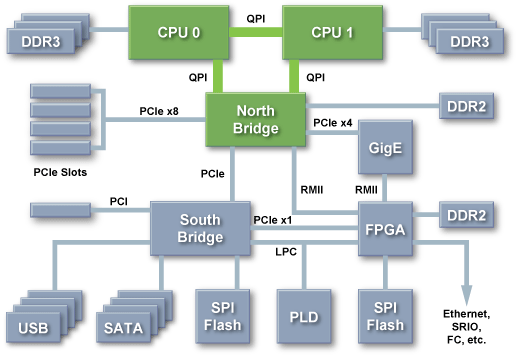

Boundary scan is the first and oldest example of an embedded instrument within silicon that is used for test purposes. Boundary scan provides a fast, effective structural (shorts and open circuits) test solution for circuit boards that lack test access. In our example here, boundary scan can provide 100% shorts and opens test coverage on the links between the CPUs and their associated links to the NorthBridge.

Boundary Scan Coverage (shown in green)

There may be some additional “pockets” of boundary scan coverage on the rest of the board depending upon its DFT, but this may be small and is very much design and component-dependent. Much of the peripheral boundary scan coverage may be only shorts coverage – that is, without coverage for opens.

More often than not, there is no boundary scan support going out to subtending PCIe buses off of the NorthBridge or SouthBridge. Many NorthBridge and SouthBridge type devices, or their terminating devices, are not compliant to the IEEE 1149.6 specification.

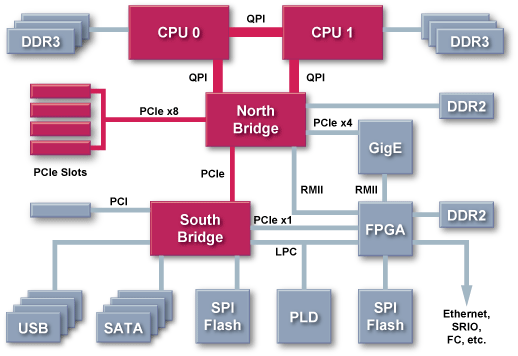

On Intel-based designs, IBIST can be used to test the QPI links between the CPUs, and between CPUs and NorthBridge, and between NorthBridge and SouthBridge. Unlike boundary scan, IBIST is an at-speed functional test, so it will detect defects that might escape boundary scan, such as solder micro-cracks or voids. On the other hand, because it operates at such a low level, doing pattern generation & checking, BERT, and margining tests, it will also provide a high level of structural test coverage – many shorts and opens will be detected by IBIST.

Intel® IBIST Coverage (shown in cerise)

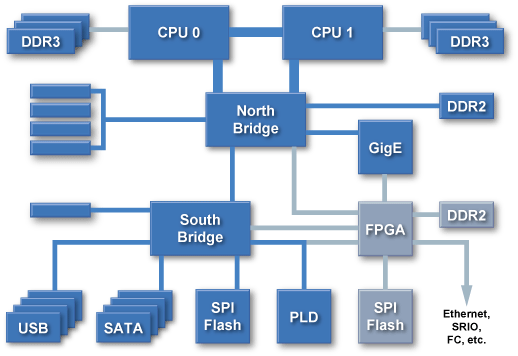

Processor-controlled test (PCT), which uses the CPU debug port to initiate register, memory and I/O reads/writes on the board, will cover a large part of the design that boundary scan and IBIST only partially touch. PCT is by far the most comprehensive of the test technologies in that anything the CPU can reach in its address space can be exercised and thereby tested. So as can be seen, much of the board can be tested by a thorough PCT test:

Processor-Controlled Test Coverage (shown in blue)

Within our circuit board block diagram, the programming model for the FPGA is considered unknown, so it would take some extra efforts to thoroughly exercise the FPGA and its subtending I/O and devices with PCT.

Finally, IJTAG, which is a synonym for the emerging IEEE 1687 standard, can provide the missing test coverage for some hard-to-reach devices and links. In our diagram, some 1687 access and control logic has been inserted into the FPGA, and a Memory Built In Self Test (MBIST) RTL instrument has been dropped into it as well. Therefore the subtending DDR2 off of the FPGA can be exercised. Try to do that with test pads or custom functional test! Similarly, the I/O off the FPGA can be tested using some I/O BIST. It would be very difficult to provide high levels of structural and functional test coverage on this part of the design without embedded instruments within the FPGA.

IJTAG Test Coverage (shown in orange)

Taken together, boundary scan + processor-controlled test + Intel IBIST + IJTAG-based MBIST and IOBIST provide a total test coverage solution for the design, without a single test point.

Combined Non-intrusive Board Test Coverage

Using iNEMI’s PCOLA/SOQ/FAM methodology (see my Blog from December 9, 2010), it can also be seen that these four technologies together will take test coverage to a much higher level.

One last thing to add: although this Blog has focused upon test coverage, there are certainly other dynamics to take into consideration when designing a manufacturing test strategy. Among them are:

- How much time does it take to develop test projects using these new technologies compared to my current approach?

- What kind of diagnostics will I get from this new approach?

- What is the test time (i.e. achievable beat rate) of a non-intrusive strategy?

- What are the economics of non-intrusive board test?

We’ll cover some of these in upcoming Blogs.

3 Responses

Alan,

In the diagram used in the example it is worth noticing that the boundary-scan capabilities on the FPGA will enable testing the DDR2’s on the FPGA, and program the SPI Flash, besides additional shorts coverage on other FPGA pins and nets.

Thanks for a nice blog!

Good observation Zed. You’re right, I was simply trying to be conservative in the representation of test coverage for the various technologies. “Your mileage may vary”, as they say.

I also observe that Intel IBIST can in most cases provide DDR3 coverage, which I left also out of the diagram. Again, it’s better to under-promise and over-deliver than the other way around! The take-away is that test coverage will vary widely based upon the characteristics of the design, which is why Test Engineering is as much an Art as a Science.

Thanks for the comments on the Blog too.

Well, this was such a good article. Very informative. Great job!