Automatically analyzing margin data on high-speed buses reduces total test times and speeds systems to market faster

The HSIO Validation Assistant (HVA), a new data mining tool for ASSET® InterTech’s ScanWorks® platform, automatically analyzes a database of signal integrity test data and quantifies the risk associated with potential design flaws or poorly performing devices on a system’s high-speed input/output (HSIO) buses.

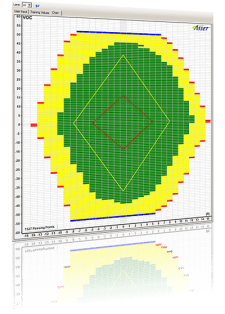

As the throughput on HSIO buses has increased, they have become more sensitive to interference and their operating margins relative to their eye masks have decreased. The slightest design or assembly flaw, or a variation in the components on the circuit board, can severely reduce HSIO throughput, possibly causing a system crash. Many silicon providers, including Intel® Corporation, have recommended an extensive battery of validation tests on all of the lanes on the serdes HSIO buses on system circuit boards. And, these tests are typically performed on multiple prototype circuit boards. The alternative validation method would be simplistic pass/fail testing, but this fails to show how close the bus signaling is to its eye mask. By knowing the operating margin and analyzing it statistically, engineers can associate a level of confidence with the system’s operations.

ScanWorks HVA automatically organizes and correlates the validation database gathered by various validation teams in the organization so engineers can efficiently identify vulnerabilities. In addition, redundant validation testing can be identified and eliminated to speed up the validation process over the life cycle of the product.

“Continually validating a system over all of its life cycle has become tremendously important and much more complicated as the speeds of HSIO buses have escalated,” said Tim Caffee, ASSET’s vice president of design validation and test. “For example, Intel might recommend that the HSIO on a design should be validated with a suite of five tests on five different prototypes. Statistically analyzing all of that test data is not straightforward, so, unfortunately some system suppliers still rely on pass/fail validation testing and that is inadequate if you want to project the risks associated with a design. HSIO Validation Assistant gives engineers the information they need in a view that makes the most sense to them.”

ScanWorks HVA has been integrated into the ScanWorks HSIO tool that validates the signal integrity on all of the high-speed buses on Intel circuit board designs, including QuickPath Interconnect (QPI), Serial Management Interface (SMI), Double Data Rate (DDR) memory bus, PCI Express (PCIe), PCIe Graphics (PEG), Direct Memory Interface (DMI), Serial ATA (SATA) and Universal Serial Bus (USB).

ASSET recently posted a new eBook on data mining an HSIO validation test database. Entitled “Data Mining Analytics for Serdes HSIO Validation,” the eBook is free and can be downloaded from the eResources section of the website.