Improvements to the graphical viewer and significantly faster performance are among the enhancements to ASSET® InterTech’s ScanWorks® IJTAG Test tool, with which engineers are able to access, control and automate the operations of test and measurement instruments embedded in chips.

ScanWorks IJTAG Test was the first suite of tools supporting the new IEEE P1687 Internal JTAG (IJTAG) standard for embedded instrumentation. IJTAG gives chip designers a more effective method for debugging chip designs by standardizing the way engineers control and access the instruments they have embedded on-chip. In addition, these same embedded instruments can be re-applied later to test, validate and debug prototypes of circuit board designs and manufactured boards.“We’ve taken the comments of our first users of ScanWorks IJTAG Test and enhanced areas of the tool where it will do the most good,” said Kent Zetterberg, technical product manager at ASSET. “We’ve found that the graphical view of the on-chip IJTAG network and providing real-time feedback to engineers as embedded instruments are running their tests are both very helpful. In addition, the speed at which ScanWorks accesses embedded instruments has increased significantly.”

Users of ScanWorks IJTAG Test have deployed the tool in a variety of applications. Some are validating IJTAG structures that have been integrated into SoCs and application-specific integrated circuits (ASIC). Others have implemented the tool in prototype circuit board bring-up and in board manufacturing. One user is employing ScanWorks IJTAG Test to access embedded instruments by way of IJTAG and other on-chip structures, such as those specified in the IEEE 1500 standard for embedded core test.

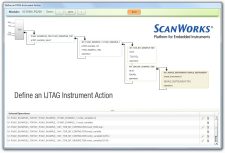

ScanWorks IJTAG Test tools can read IJTAG’s two languages, Instrument Connectivity Language (ICL) and Procedural Description Language (PDL). ICL defines the access connections for the instruments embedded on-chip while PDL is an extension of the popular Tcl (Tool Command Language) for programming validation, test and debug vectors to be executed by embedded IJTAG instruments. With the graphical user interface on ScanWorks IJTAG Test engineers can drag-and-drop instruments and specific operations to automatically develop test routines.

The IJTAG standard recently passed a significant milestone on the road to approval. In advance of its going to ballot, the draft of the specification has been submitted to the IEEE’s Mandatory Editorial Coordination (MEC) process, which determines whether the draft of the specification conforms to the IEEE’s editorial requirements. Following the MEC review, IEEE balloting to ratify the IJTAG standard can begin.

“Clearing the MEC hurdle will be very encouraging. We will be that much closer to ratification,” said Ken Posse of Avago Technologies, chairman of the IEEE P1687 working group that is developing the IJTAG standard. “We could not have gotten this far without the help of people like Al Crouch of ASSET InterTech who has been the working group’s vice chairman. Another encouraging aspect of IJTAG is the rapid rise of an ecosystem around the standard. We’ve seen chip design companies like Mentor step up with insertion tools and, of course, ASSET’s ScanWorks tools have helped demonstrate the value of an open industry standard for embedded instruments.”

More information on the IJTAG standard can be found in the ebook “How to use embedded instruments and JTAG/IJTAG – An IEEE P1687 Tutorial”.