IEEE P1687 IJTAG standard simplifies and automates management of embedded on-chip instruments.

Richardson, TX (August 23, 2012) – A new introductory tutorial from ASSET® InterTech (www.asset-intertech.com), the leading supplier of tools for embedded instrumentation, explains how the new IEEE P1687 Internal JTAG (IJTAG) standard simplifies and automates the way chip designers manage embedded instruments which perform chip validation and characterization.

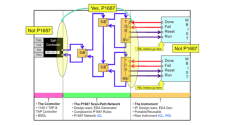

The IJTAG standard, which is expected to be voted on later this year via the IEEE’s normal standards process, specifies a standard interface to instruments embedded in chips, and defines a methodology for accessing them, automating their operations and analyzing their outputs. To allow for a wide variety of functionality, an instrument’s core intellectual property (IP) does not need to conform to the IJTAG standard, just the instrument’s interface to the on-chip IJTAG network. With standardized embedded instrumentation chip designers are better able to manage the hundreds or thousands of instruments that are typically embedded in complex components and systems-on-a-chip (SoC). The standard defines an architecture that can automatically connect all IJTAG instruments as well as an access methodology for automating their operations.

“Several chip companies have already realized the value of the IJTAG standard and how it will be a boon to their customers, the system suppliers,” said Al Crouch, ASSET’s chief technologist for core instruments and a co-chairman of the IEEE IJTAG working group that is developing the standard. “Not only does it simplify and accelerate the chip designer’s job when it comes to validating and debugging chips, but later in the life cycle those same embedded instruments can be re-used by board-level manufacturers to validate, test and debug circuit boards. IJTAG reduces time-to-market, streamlines part of the design process and cuts test costs for both chip vendors and board manufacturers.”

ASSET’s IJTAG Tutorial describes the on-chip IJTAG architecture as well as the two languages defined by the standard, Instrument Connectivity Language (ICL) and Procedural Description Language (PDL). ICL defines the connections among embedded on-chip instruments and PDL is an extension of the popular Tcl (Tool Command Language) for developing validation, test and debug vectors for execution by IJTAG instruments.

The tutorial can be downloaded directly from the ASSET web site IJTAG-Tutorial.

About ASSET InterTech

ASSET InterTech is the leading supplier of tools for embedded instrumentation for design validation, test and debug. The ScanWorks® platform for embedded instruments provides automation, access and analysis tools in one environment. Users can quickly and easily validate and test semiconductors, circuit boards or entire systems during every phase of a product’s life, including design, manufacturing/repair and field maintenance. ASSET InterTech is located at 2201 North Central Expressway, Suite 105, Richardson, TX 75080.

For product information, call 888-694-6250, fax 972-437-2826, e-mail ai-info@asset-intertech.com or visit www.asset-intertech.com.

Trademarks: ASSET and ScanWorks are registered trademarks while the ASSET logo is a trademark of ASSET InterTech, Inc. All other trade and service marks are the properties of their respective owners.