ScanWorks IJTAG Test

About ScanWorks IJTAG Test

Interact with your instruments

The ScanWorks® Internal JTAG (IJTAG) tools allow system-on-a-chip (SoC) designers, DFT engineers and validation engineers a new and simpler way to access, control and run any embedded instrument designed into chips. The IEEE 1687-2014 Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device defines a scalable and reusable methodology to operate embedded instruments.

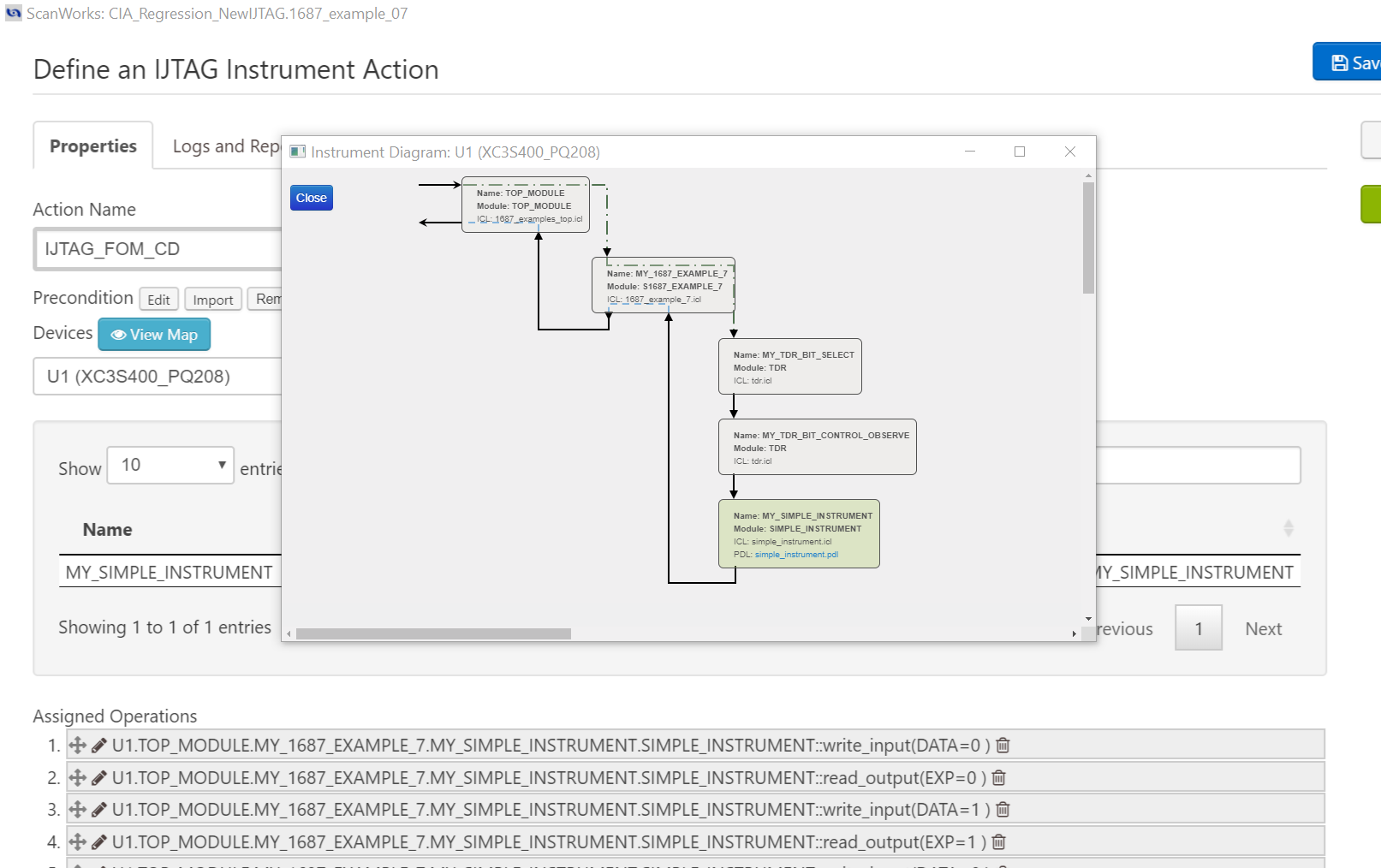

ScanWorks IJTAG products read the IJTAG standard’s Interconnect Connectivity Language (ICL) and from that determines where all the instruments in the chip are. Then ScanWorks uses the IJTAG standard’s other language, Procedural Description Language (PDL), to run the embedded instruments that have been selected to solve the problem at hand. ScanWorks IJTAG Test operation is driven by the DFT engineer or board test developer and the ICL/PDL content. The test developer has total control over enabling access to the instruments via IJTAG bus.

Currently, tools to control embedded instruments, if they exist at all, are usually proprietary to a certain technology. As a result, the engineer would need multiple tools and multiple access mechanisms, or he would have to develop his own tools. The IJTAG standard and ScanWorks IJTAG chip test and debug tools provides a simple yet elegant solution to solve this problem.

Software – driven instruments

The ScanWorks® Internal JTAG (IJTAG) tools allow system-on-a-chip (SoC) designers, DFT engineers and validation engineers a new and simpler way to access, control and run any embedded instrument designed into chips. The IEEE 1687-2014 Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device defines a scalable and reusable methodology to operate embedded instruments. ScanWorks IJTAG Test tools are another non-intrusive validation, test or debug technology for the ScanWorks platform for embedded instruments. Semiconductor companies can use ScanWorks IJTAG tools to develop and/or process ICL and PDL content during first silicon bring-up to verify in situ access and operation of embedded instruments that are critical to the success of their customers board applications. Once silicon ramps into production, the manufacturing flow of the chip can utilize the ScanWorks Platform to re-use the ICL and PDL content during QA gates as well as burn-in oven stimulus.

Once a chip leaves the semiconductor manufacturer and is designed into a circuit board, the board designer can re-use the same ScanWorks IJTAG tools, as well as the same ICL and PDL content for the embedded instruments, to validate, test and debug the board itself, should the board’s test strategy call for this and the embedded instruments possess the test capabilities needed. In addition, the semiconductor manufacturer can work with their customers to perform in situ fault diagnostics during board bring-up as well as board failures in the field. These capabilities enable valuable synergy between an SoC supplier and its customer. When a difficult problem is found, the supplier and customer can use the same tools, work together and share data to solve product integration problems quickly.

Find out more about why both chip and board designers should use IJTAG (IEEE 1687).

IJTAG Test Development Software

The ScanWorks® IJTAG Test Development Software is a semi-automated and extremely flexible methodology for accessing and controlling embedded instruments in system-on-a-chip (SoC) designs to help debug these very complex devices. To get started, ScanWorks simply reads-in the IJTAG Interconnect Connectivity Language (ICL) and Procedural Description Language (PDL) files. ScanWorks then displays all the instructions and functions that each instrument can perform. All the engineer does is drag and drop the sequence of events and tests he wants the instruments to perform. It’s that simple!

Once satisfied with the test program for a certain instrument, the developer just clicks Run and the instruments embedded in the SoC are automatically test the device.

Features

- Validate, test and debug complex SoCs within one environment using all the IJTAG instruments designed into the chip.

- Accelerate debug and test times by running multiple instruments concurrently.

- Validate instruments and perform tests right from the chip designer’s desk. No need to fight for precious and expensive IC ATE tester time.

- Easily integrate into a load board to complement IC ATE.

- Empower the SoC customer – the board designer – with the same tools that were used by the chip designer. Shorten the board designer’s board bring-up cycles by leveraging instruments embedded in the SoC. This adds even more value to the SoC.

Find out more about why both chip and board designers should use IJTAG (IEEE 1687).

IJTAG Test Manufacturing Software

For the SoC Developer, ScanWorks IJTAG Test Manufacturing software can be used stand-alone or as a complement to IC ATE via a connection to the chip-under-test on a load board. Thus, IC ATE focuses on what it does best and IJTAG test capabilities are added at a very low cost.

For the SoC Customer doing Board Test, The SoC user who is re-using some of a chip’s embedded instruments in manufacturing board test can add an IJTAG Test Manufacturing license to the other applications deployed on any ScanWorks platforms already performing manufacturing test. The IJTAG test applications complete the ScanWorks board test capabilities by covering issues concerning specific SoCs. In addition, when problems arise and boards must be diagnosed, another tool is available within the ScanWorks environment.

Features

- Re-use ScanWorks IJTAG test instruments that were employed during SoC test and board bring-up

- Extend test coverage for SoCs by complementing IC ATE and for board test as another ScanWorks application

- Utilize as a data collection instrument engine for characterization, failure analysis and yield analysis during the SoC process

- Run any instrument on the IJTAG network in the chip with the built-in PDL engine

Related Products

The ScanWorks platform for embedded instruments is supported by a wide variety of hardware controllers and accessories with which engineers can connect ScanWorks to their unit under test (UUT). Hardware is available for development, production and repair environments. The test platform required for ScanWorks is either a standard PC or a system with a built-in (embedded) JTAG controller.

Related eResources

Accessing and operating embedded instrument IP has not been easy. In fact, it’s been a challenge. But the recently ratified IEEE 1687 Internal JTAG (IJTAG) standard for embedded instruments is changing the way the industry thinks about chip characterization and debug, portable IP, re-targeting test vectors, embedded TAPs, on-chip instrument networks, and how to re-use all that instrumentation embedded in chips to validate, test and debug not only chips, but circuit boards as well.